GPIO

简介

General Purpose Input Output,即通用输入输出端口,简称GPIO- 作用:负责采集外部器件的信息或者控制外部器件工作,即输入输出

GPIO特点

- 不同型号,

IO口数量可能不一样- 快速翻转,每次翻转最快只需要两个时钟周期

- 每个10口都可以做中断

- 支持8种工作模式

电器特性

- 工作电压

VDD:2.0~3.6V,通常使用3.3V- 逻辑电平(输入识别)

- CMOSE

- 低电平VIL:-0.3V ~ 0.3 * VDD

- 高电平VIH:0.7 * VDD ~ VDD + 0.3V

- 5V容忍引脚(FT)

- 低电平VIL:-0.3V ~ 0.3 * VDD

- 高电平VIH:0.7 * VDD ~ 5.0V

- 输出:单个

IO,最大25mA

引脚类型

- 电源引脚(VXX)

- 晶振引脚(高速低速两组输入输出)

- 复位引脚(NRST)

- 下载引脚

- BOOT引脚(BOOTX)

- GPTO引脚(PXX)

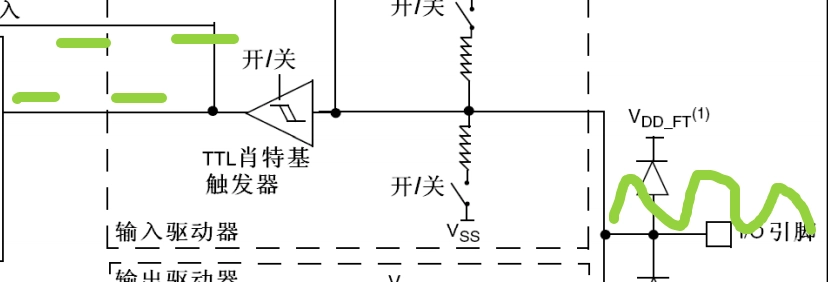

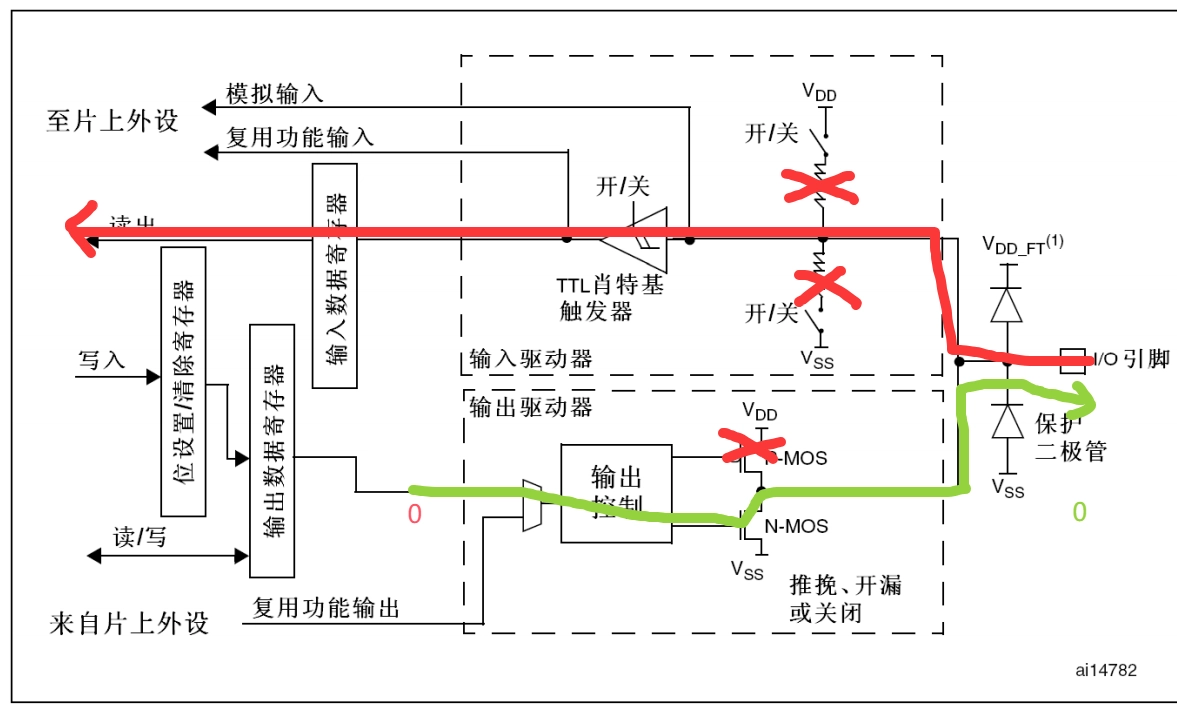

IO端口结构

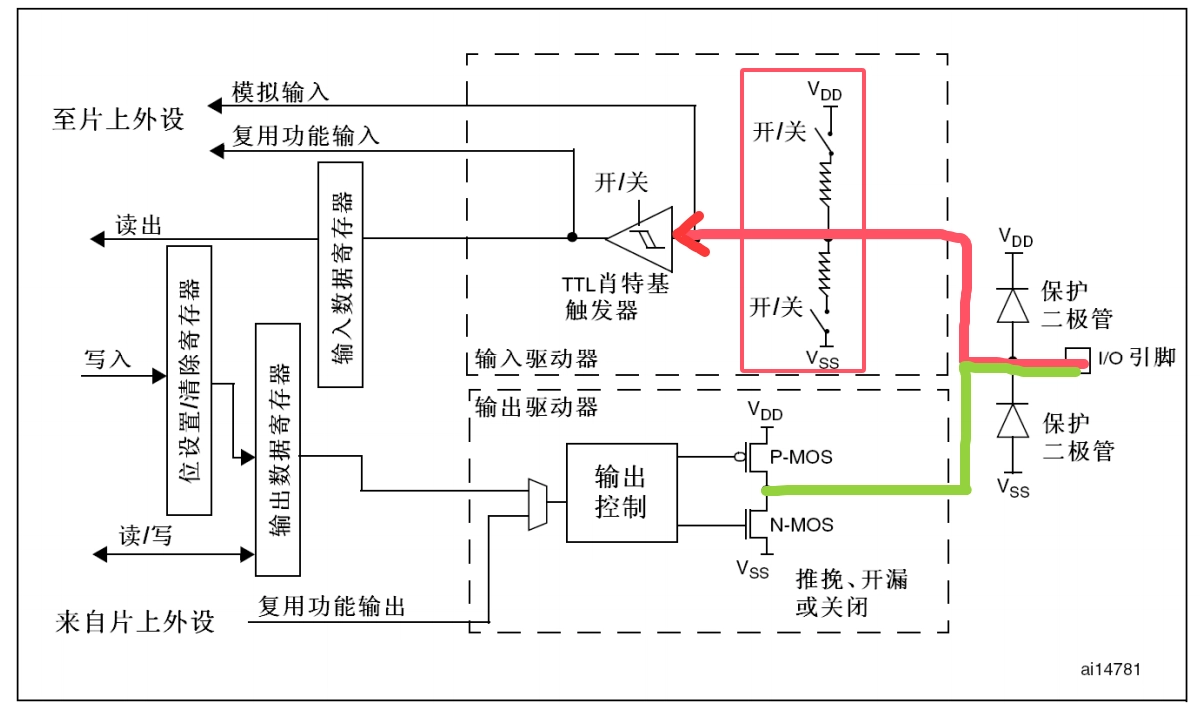

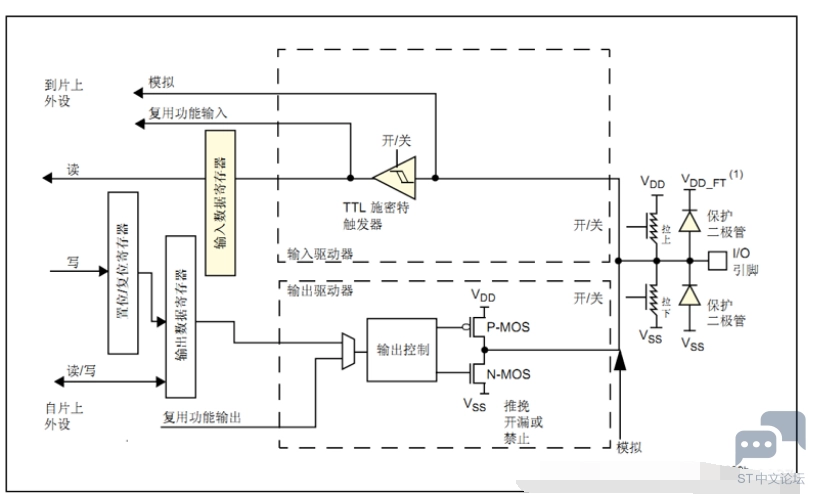

原理图

- 上图为F1,其它系列如下图

- 区别在于F1只能在输入时可以选择使用上拉还是下拉电阻

- 其他系列输入输出都可以选择使用上拉或下拉电阻

输入分析

保护二极管

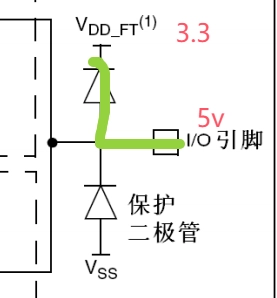

以外部IO输入高电平5v为例

- 上方的二极管导通,电流过大烧坏,5v进入IO内部会烧毁其它组件(高于安全电压)

- 实际使用应该在IO引脚机上接限流电阻,内部电压:VDD(3.3)+二极管(0.3)=3.6V,安全

上拉/下拉电阻(可选)

接上拉电阻

- 如果IO口外部没有信号输入或者引脚悬空,IO口默认为高电平

- 如果I/O口输入低电平,那么引脚就为低电平,MCU读取到的就是低电平

- 实际是弱上拉,电流很小,非悬空则取决于外部

接下拉电阻

- 如果IO口外部没有信号输入或者引脚悬空,IO口默认为低电平

- 如果I/O口输入高电平,那么引脚就为高电平,MCU读取到的就是高电平

施密特/肖特基触发器

- 将模拟信号转数字信号

- 在高阈值以上为高,低阈值以下为低,中间则保持之前的

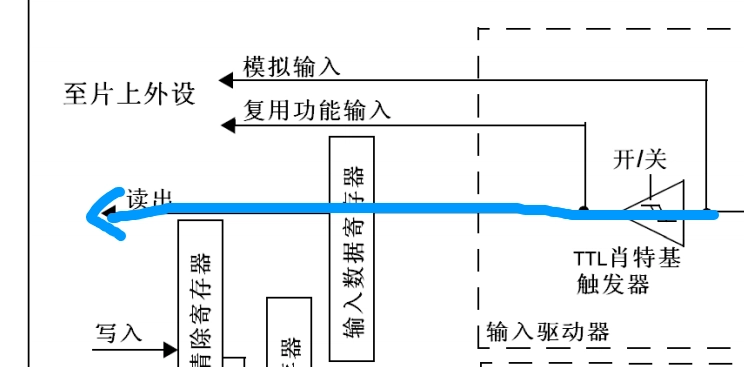

最终输入

- 模拟输入:adc,dac

- 复用功能输入:UART,I2C,SPI等

- 输入寄存器(IDR)输入:普通GPIO功能,引脚的数字信号(0,1)

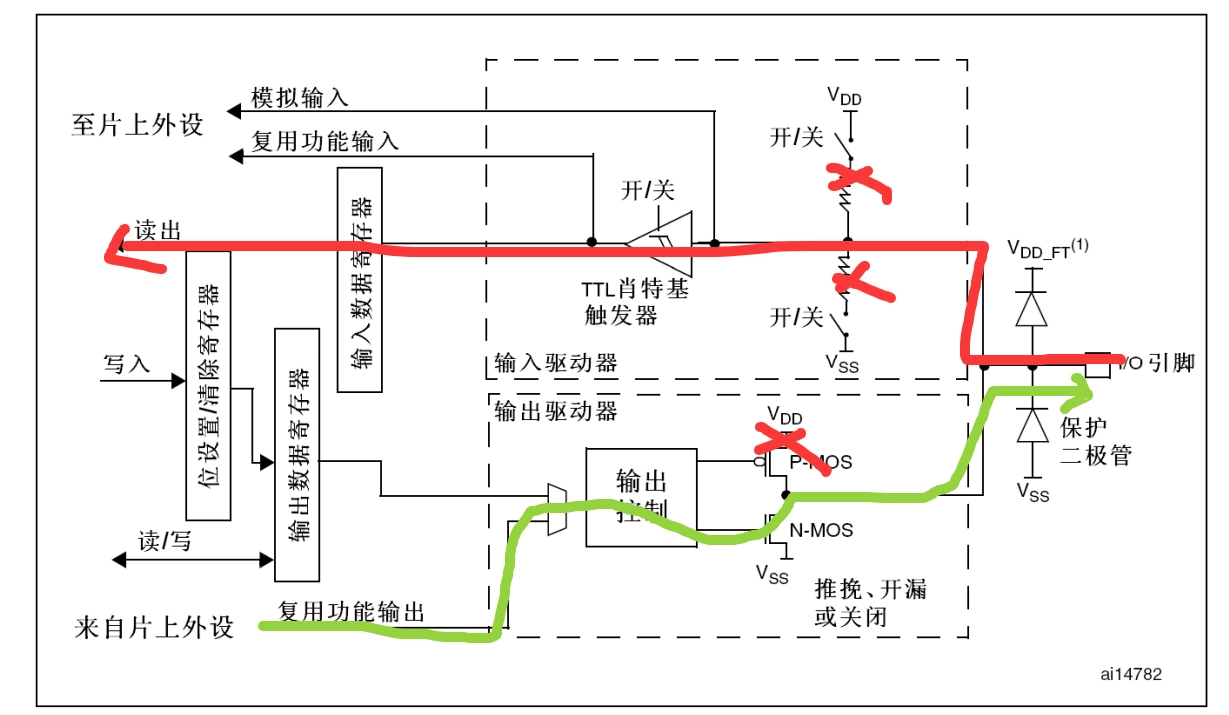

输出分析

输入

通用输入有两条路

- 通过为设置清楚寄存器,间接操作输出寄存器(QDR)

- 直接操作输出寄存器

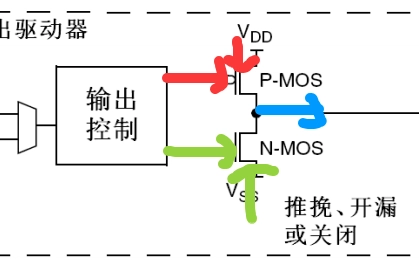

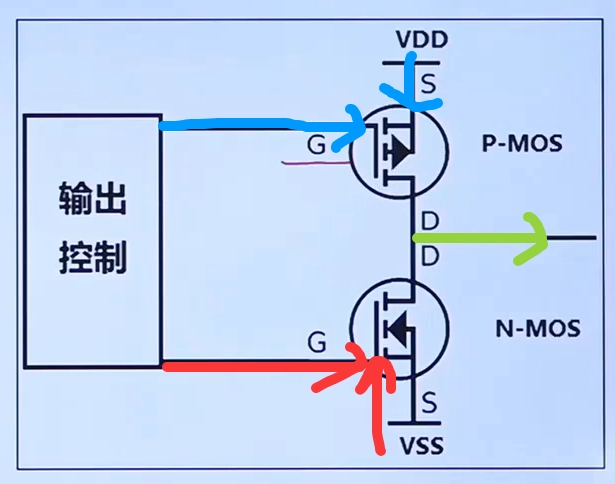

MOS管

等效电路,VDD(3.3),VSS(0),Vgs=Vg-Vs

- P-MOS管,Vgs<0导通,通用输入输出S=1,只需要G=0则导通,导通则外部为VDD的1

- N-MOS管,Vgs>0导通,通用输入输出S=0,只需要G=1则导通,导通则输出为VSS的0

总之不同就导通

八种工作模式

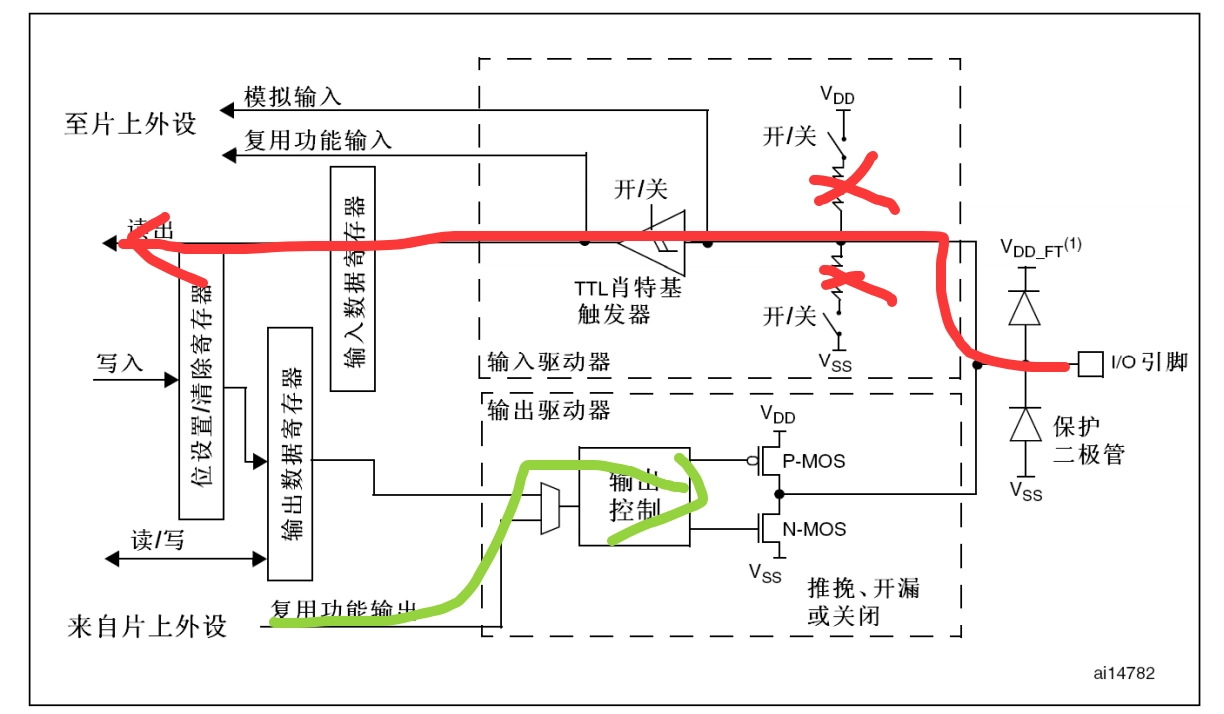

四种输入

- 输入时,输出的P-MOS都是不导通的(GS相同)

- 分析与前面的输入分析一致

| 输入模式 | 特点 |

|---|---|

| 输入浮空 | 引脚浮空(即高组态),状态不定 |

| 输入上拉 | 使用内部上拉电阻,默认(高组态)高电平,否则取决于外部 |

| 输入下拉 | 使用内部下拉电阻,默认(高组态)低电平,否则取决于外部 |

| 模拟输入 | 通用GPIO无效,用于ADC、DAC外设 |

四种输出

| 输出模式 | 特点 |

|---|---|

| 开漏输出 | 软件IIC |

| 推挽输出 | 驱动能力强,通用输出 |

| 复用开漏输出 | 片上外设功能(硬件IIC) |

| 复用推挽输出 | 片上外设功能(SPI) |

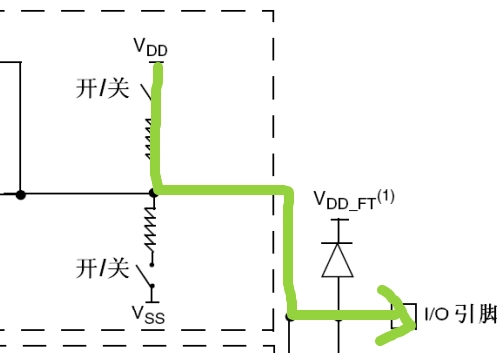

开漏输出分析

P-MOS始终关闭,输出控制添加一个VDD实现

输出0则下方N-MOS导通【通过输出控制处理,如反向器】,最终输出0

输出1,N-MOS不导通,输出悬空,是高组态。可以通过IO引脚外接上拉电阻实现输出1

或者内部外接上拉电阻实现,当然F1输出不能使用,使用其他系列可以使用

复用开漏输出

参考开漏输出

- 要输出高电平也是需要上拉电阻

- 其他输出由外设控制

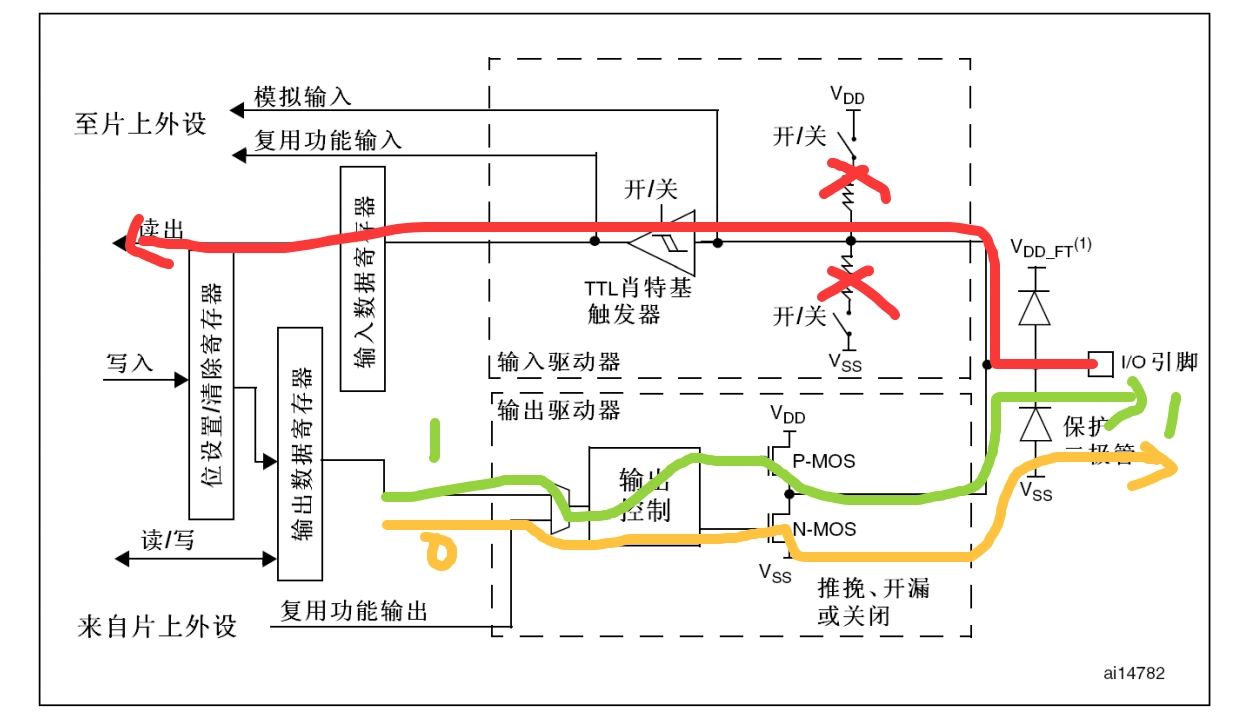

推挽输出

1则P-MOS导通,输出1

0则N-MOS导通,输出0

驱动能力强(并没有电阻限流,直接接入VSS或VDD)

输出控制使用反向器即可实现

复用推挽输出

参考推挽输出

- 驱动能力强

- 输出取决于外设

GPIO输出速度

基于2MHz、10MHz和50MHz频率。

“速度”指的是输出驱动电路的响应速度,并不是输出信号的速度。

应该根据需求选择相匹配的驱动电路,达到最佳的噪声控制效果,并降低功耗。

- 对于LED、数码管、蜂鸣器等低速设备,一般设置2MHz;

- 对于串口,一般2MHz引脚速度;

- 对于I2C接口,可以选用10MHz的引脚速度;

- 对于SPI接口,可以选择50MHz的引脚速度。

- 对于复用功能的,一般设置50MHz的引脚速度。

输入不用管